介電常數

| 介電常數 |

|

介電常數,介質在外加電場時會產生感應電荷而削弱電場,介質中的電場減小與原外加電場(真空中)的比值即為相對介電常數(relative permittivity或dielectric constant),又稱誘電率,與頻率相關。介電常數是相對介電常數與真空中絕對介電常數乘積。如果有高介電常數的材料放在電場中,電場的強度會在電介質內有可觀的下降。理想導體的相對介電常數為無窮大。

簡介

相對介電常數εr可以用靜電場用如下方式測量:首先在兩塊極板之間為真空的時候測試電容器的電容C0。然後,用同樣的電容極板間距離但在極板間加入電介質後測得電容Cx。然後相對介電常數可以用下式計算

εr=Cx/C0

在標準大氣壓下,不含二氧化碳的乾燥空氣的相對電容率εr=1.00053.因此,用這種電極構形在空氣中的電容Ca來代替C0來測量相對電容率εr時,也有足夠的準確度。(參考GB/T 1409-2006)

對於時變電磁場,物質的介電常數和頻率相關,通常稱為介電係數。

評價

近十年來,半導體工業界對低介電常數材料的研究日益增多,材料的種類也五花八門。然而這些低介電常數材料能夠在集成電路生產工藝中應用的速度卻遠沒有人們想象的那麼快。其主要

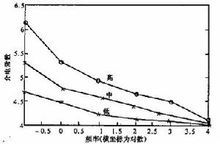

原因是許多低介電常數材料並不能滿足集成電路工藝應用的要求。圖2是不同時期半導體工業界預計低介電常數材料在集成電路工藝中應用的前景預測。

早在1997年,人們就認為在2003年,集成電路工藝中將使用的絕緣材料的介電常數(k值)將達到1.5。然而隨着時間的推移,這種樂觀的估計被不斷更新。到2003年,國際半導體技術規劃(ITRS 2003[7])給出低介電常數材料在集成電路未來幾年的應用,其介電常數範圍已經變成2.7~3.1。

造成人們的預計與現實如此大差異的原因是,在集成電路工藝中,低介電常數材料必須滿足諸多條件,例如:足夠的機械強度(MECHANICAL strength)以支撐多層連線的架構、高楊氏係數(Young's modulus)、高擊穿電壓(breakdown voltage>4MV/cm)、低漏電(leakage current<10-9 at 1MV/cm)、高熱穩定性(thermal stability >450oC)、良好的粘合強度(adhesion strength)、低吸水性(low moisture uptake)、低薄膜應力(low film stress)、高平坦化能力(planarization)、低熱漲係數(coefficient of thermal expansion)以及與化學機械拋光工藝的兼容性(compatibility with CMP process)等等。能夠滿足上述特性的完美的低介電常數材料並不容易獲得。例如,薄膜的介電常數與熱傳導係數往往就呈反比關係。因此,低介電常數材料本身的特性就直接影響到工藝集成的難易度。

目前在超大規模集成電路製造商中,TSMC、 Motorola、AMD以及NEC等許多公司為了開發90nm及其以下技術的研究,先後選用了應用材料公司(Applied Materials)的Black Diamond 作為低介電常數材料。該材料採用PE-CVD技術[8] ,與現有集成電路生產工藝完全融合,並且引入BLOk薄膜作為低介電常數材料與金屬間的隔離層,很好的解決了上述提及的諸多問題,是目前已經用於集成電路商業化生產為數不多的低介電常數材料之一。[1]